通讯协议--LPC通讯初步认识

通讯协议

CPU如何通过LPC访问EC

LPC(Low Pin Count)是一种低引脚数的总线协议。在主板上,除了CPU、DDR、PCIe这些高速设备外,还有很多低速控制设备例如:键盘、风扇、电源、电池管理。这些功能通常由一个芯片负责——EC(Embedded Controller)。

CPU 如何与 EC 这样的低速设备通信?

主要就是通过LPC总线,主要用于连接以下设备:

EC(Embedded Controller)

Super I/O

BIOS Flash 等低速设备

LPC与EC的地址映射

在操作系统或固件看来,CPU是通过访问I/O地址来与外设通信的。

EC 通常使用下面两个端口:

1 |

CPU在固件或操作系统中访问EC时,本质上只是对这些端口进行读写,例如:

1 | // 读 |

但EC并不直接连接到CPU的I/O总线,而是挂在LPC总线上。

1 | CPU |

CPU并不知道EC的内部结构,EC在主机系统中更像是一个“可编程外设”,类似EEPROM这种,可以读写。

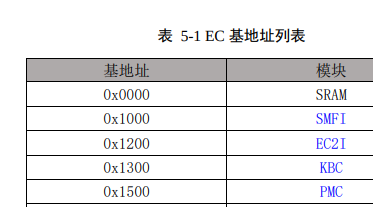

EC 内部地址空间

EC本身通常是一个嵌入式MCU,可能是8位也可能是32位的专用芯片。EC固件会将部分内部地址映射到 LPC访问接口,供 CPU访问。

| EC 内部地址 | 功能 |

|---|---|

| 0x0000 – 0x0FFF | EC SRAM |

| 0x1000 – 0xFFFF | 设备其他控制寄存器 |

文档示例:

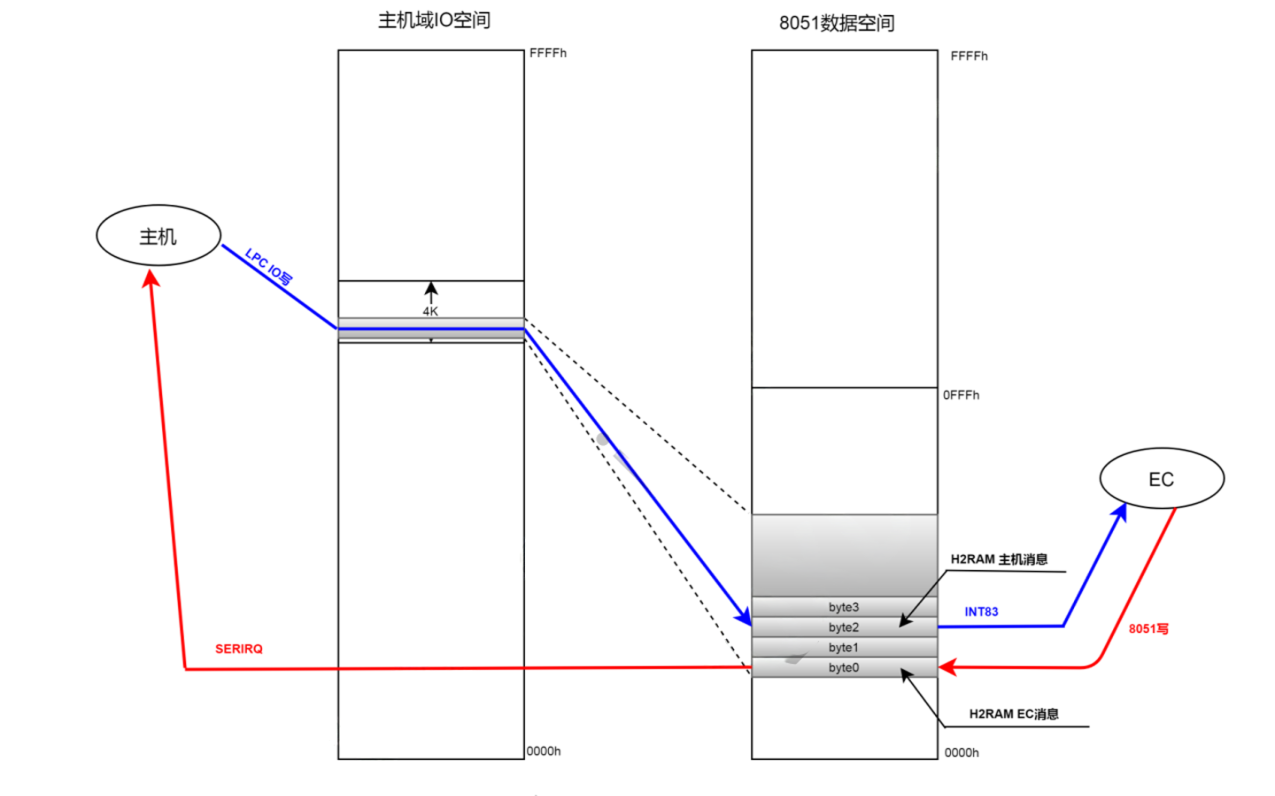

可以这么理解,LPC端口是EC内部地址空间的访问入口。交互示意图如下:

信号定义

LPC 接口由7个必选信号 + 6 个可选信号组成,多数信号与 PCI 复用,无需主机新增引脚。

| 信号类型 | 核心信号 | 核心功能 |

|---|---|---|

| 必选信号 | LAD[3:0] | 分时复用传输命令、地址、数据 |

| LFRAME# | 标识新周期开始、中止错误周期 | |

| LRESET# | 复位信号,与 PCI 复位同源 | |

| LCLK | 时钟信号,通常与 PCI 时钟同步 | |

| 可选信号 | LDRQ# | DMA / 总线主设备请求,每个外设独立,不可共享 |

| SERIRQ | 串行中断,替代传统 ISA 中断线 | |

| LPCPD# | 电源关断,通知外设准备断电 | |

| LPME# | 电源管理事件,请求从低功耗唤醒 |

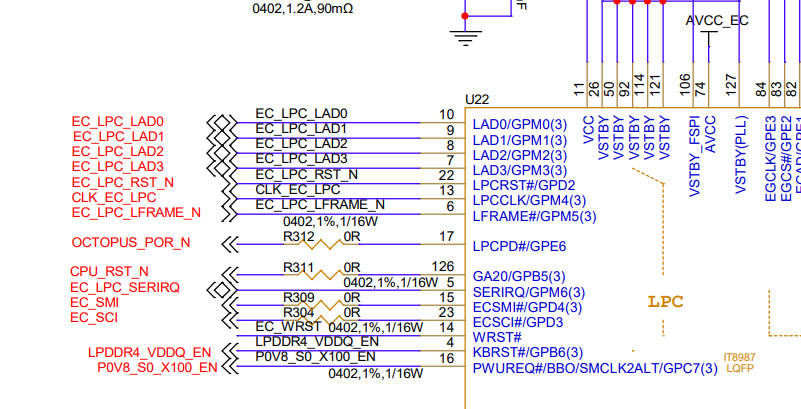

如下设计:

LPC 的特点是:地址、命令、数据都通过LAD[3:0]分时传输。

本文简单的介绍了LPC总线的基本概念、EC地址映射关系以及核心信号定义,后续我可能会进一步分析LPC的通信原理和时序机制,包括读写周期与通信流程。

评论