通讯协议--LPC通讯流程与时序

通讯协议

LPC协议

上次初步介绍了LPC总线协议,以及CPU是如何通过LPC访问EC的。这次主要总结下LPC完整通讯流程和时序。

通讯流程与时序

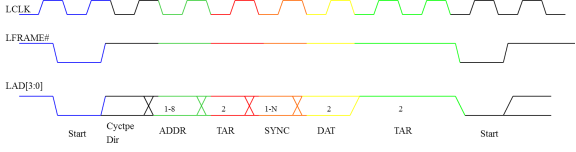

LPC是一个同步协议,所有的信号采样都在LCLK的上升沿。通讯以“Cycle(周期)”为单位。

cycle示意流程图 :

想了解更深可以参考以下文档:

Intel LPC Interface Specification

一个典型的I/O读写周期包含以下阶段:

1、Start(1 clock): 主设备(CPU/PCH)将LFRAME#拉低,并在LAD[3:0] 上输出开始状态0000,表示一个周期的开始。当FRAME#信号有效时,所有的外设都要监视LAD[3:0]信号。

2、Cycle Type/Dir (1 clock): 告知是读还是写,以及访问类型(I/O, Memory, DMA),LAD[0]在该场中被保留,作为外设应该忽略。

3、Address (8 clocks):Memory访问:32 位地址,占用 8 时钟;I/O访问:16 位地址,占用 4 时钟

4、TAR (Turn-around, 2 clocks): 交换总线的控制权,这是“换手”阶段,防止两个设备同时驱动总线导致短路,谁需要交还控制权,谁驱动LAD [3:0]保持1111。

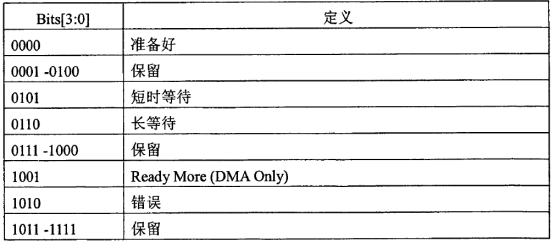

5、SYNC (Variable): 等待从设备响应。在target或者DMA传输操作时,Sync由外设驱动;在bus master操作时,Sync由Host驱动。外设未就绪时可插入等待,准备好后回复0000表示就绪。

6、Data (2 or 8 clocks): 传输数据。如果是写,由主设备驱动;如果是读,由从设备(EC)驱动。

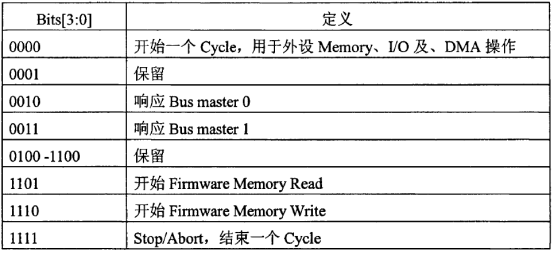

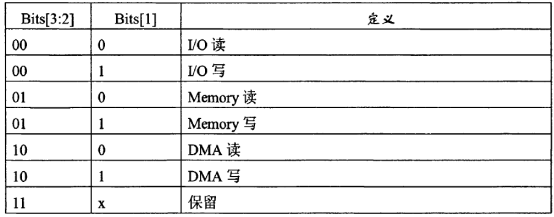

以下列表中Bits[3:0]表示LAD[3:0]位变化

Start状态定义:

Cyctype IR状态定义:

Sync状态定义:

通讯示例

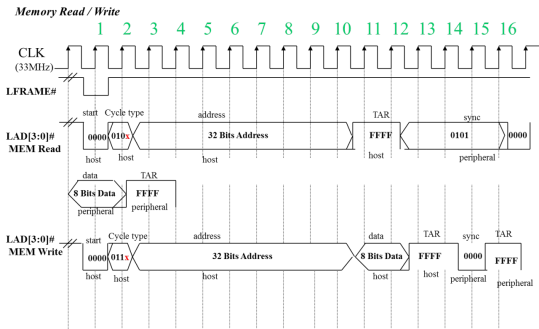

Memory 读写时序参考:

内存读写先后顺序解答,从左往右看:

- 主机把LFRAME#低,LAD按照上面start信号控制,如memory读

010x. - 主机传32位I/O地址

- 主机释放总线,给设备

- 从机如果就绪=0000/等待=0101

- 从机开始读写数据

- 从机释放总线,给主机

- 主机开始LFRAME#高

总结

本文重点讲解LPC 协议的周期结构、信号含义、I/O 读写时序,配合时序图与流程图,可快速理解其工作原理。因为LPC现在比较成熟,厂商已提供成熟驱动与代码,以上了解即可。

下次我应该还会从寄存器、端口访问到完整驱动代码,分享一些CPU与EC的LPC通信实战调试内容。